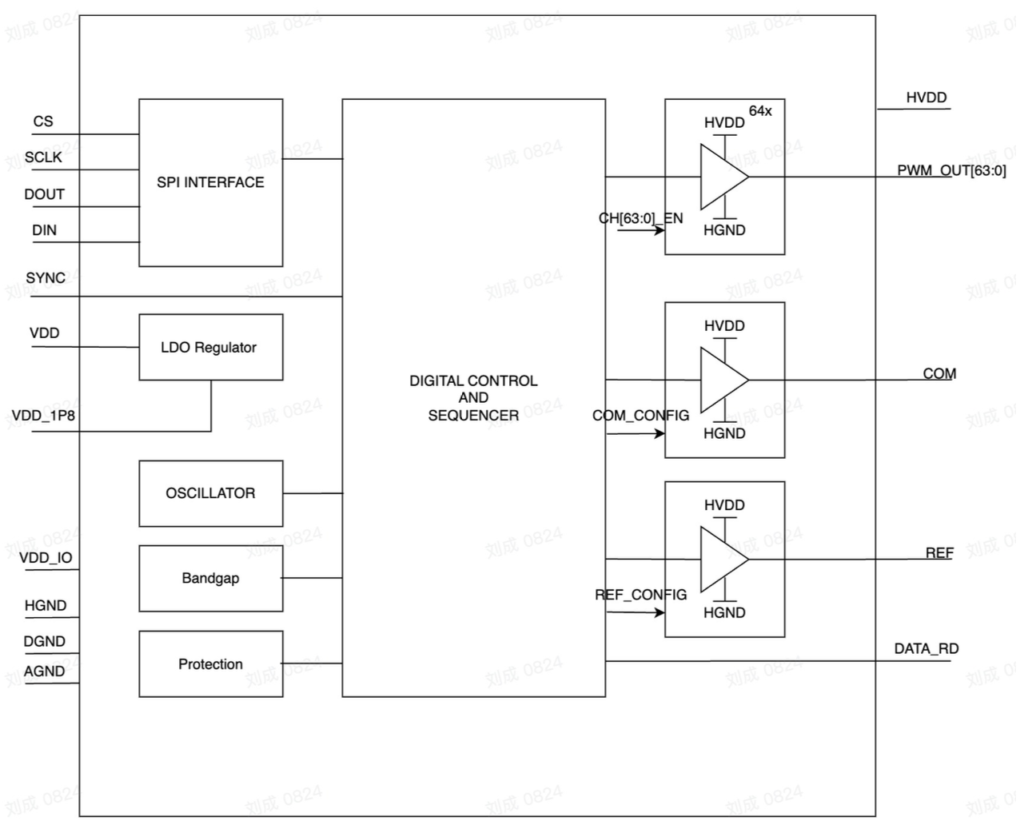

MCAD0641 is an optical phased array driver for liquid crystal metasurface. It generates up to 64-channels of programmable square wave signal to realize the beam steering, and each channel can be controlled independently and activated at the same time.

The output driver capability could be configured to obtain the best response time by providing up to 16 different selections.

A unique diagnose circuit is also embedded to check that the short-circuit conditions of the optical phased array, and then the user could disable the failed channel selectively.

The built-in over-drive function can fasten the response time of the optical phased array. The square wave generator can run up to 78.12kHz with 8 different setting.

The SPI interface provides the maximum applicable flexibility of MCAD0641, and the controlled phase data is transmitted through SPI communication.

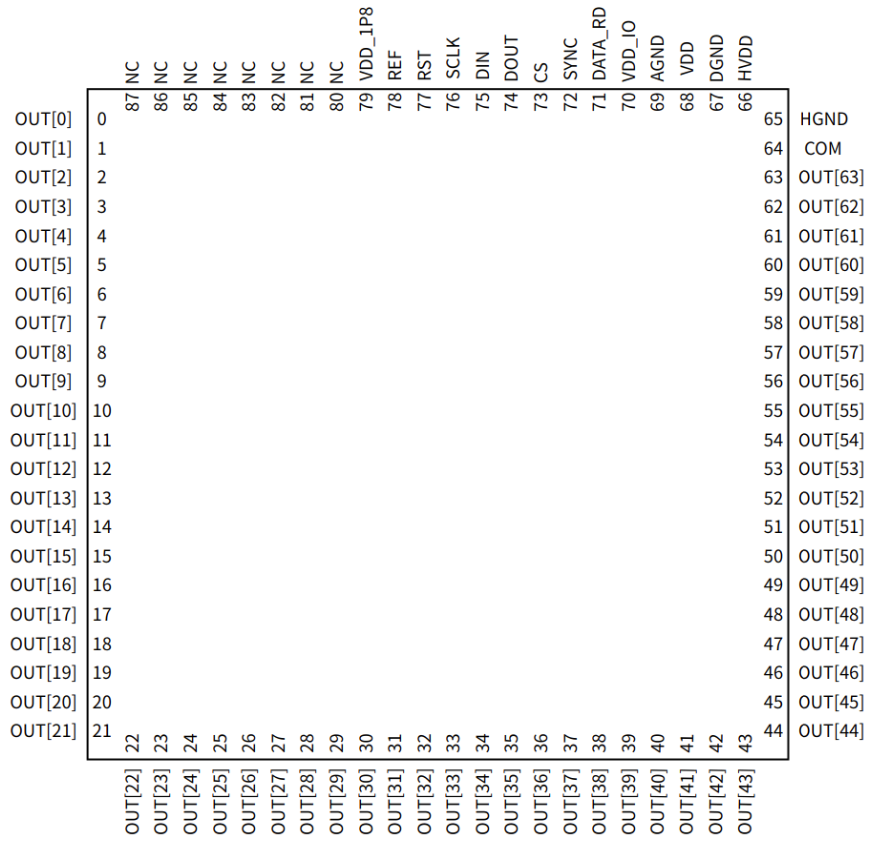

| Pin No. | Pin name | Supply class | Pin type | Description |

|---|---|---|---|---|

| 0 ~ 63 | OUT [0] ~ OUT [63] | HVDD | AO | Square wave output channel |

| 64 | COM | HVDD | AIO | IO that can be configured for different case |

| 65 | HGND | HGND | PWR | High voltage supply ground pin, must be connected to other ground externally |

| 66 | HVDD | HVDD | PWR | High voltage supply pin |

| 67 | DGND | DGND | PWR | Digital supply ground pin, must be connected to other ground externally |

| 68 | VDD | VDD | PWR | Digital supply pin for digital core |

| 69 | AGND | AGND | PWR | Analog supply ground pin, must be connected to other ground externally |

| 70 | VDD_IO | VDD_IO | PWR | Supply pin for input & output interface |

| 71 | DATA_RD | VDD | DO | Data ready signal. Driver sends to MCU to indicate that the square wave signal is ready to send out. Only used for debug. |

| 72 | SYNC | VDD | DI | Signal received from MCU to load the PWM data of 64 sets in register to output. |

| 73 | CS | VDD | DI | Chip select of SPI |

| 74 | DOUT | VDD | DO | Serial Data Output of SPI, send out the data on the rising edge of SCLK |

| 75 | DIN | VDD | DI | Serial Data Input of SPI, sampled into the device on the falling edge of SCLK |

| 76 | SCLK | VDD | DI | Serial Clock of SPI |

| 77 | RST | VDD | DI | Chip Reset |

| 78 | REF | HVDD | AI | Reflection layer |

| 79 | VDD_1P8 | VDD_1P8 | PWR | 1.8V LDO output, placed with 4.7uF ceremic cap. |

| 80 ~ 87 | NC | N/A | N/A | N/A |

| Parameter | MIN | MAX | UNIT |

|---|---|---|---|

| Supply voltage (VDD) | -0.3 | 6.0 | V |

| Supply voltage (HVDD) | -0.3 | 15.0 | V |

| Supply voltage (VDD_IO) | -0.3 | 6.0 | V |

| Decouple output voltage (VDD_1P8V) | -0.3 | 6.0 | V |

| Logic input voltage (CS, SCLK, DIN, RST) | -0.3 | 6.0 | V |

| Logic output voltage (SYNC, DOUT, DATA_RD) | -0.3 | 6.0 | V |

| Driver output voltage (OUT [0] ~ OUT [63]) | -0.3 | 15 | V |

| COM | -0.3 | 15 | V |

| REF | -0.3 | 15 | V |

| Junction temperature range, TJ | -40 | 150 | ̊C |

| Storage temperature | -65 | 150 | ̊C |

| VALUE | UNIT | ||

|---|---|---|---|

| ESD (Electrostatic discharge) | Human-body model, per ANSI/ESDA/JEDEC JS-001m, all pins | +/-2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101, all pins | +/-500 | V |

| Items | Parameters | MIN | NOM | MAX | UNIT |

|---|---|---|---|---|---|

| Supply voltage range | VDD | 4.5 | 5.5 | V | |

| HVDD | 5 | 10 | 12 | V | |

| VDD_IO | 1.6 | 5.5 | V | ||

| Operating free-air temperature, TA | -40 | 25 | 85 | °C |

VDD = VDD_IO = 3.3V, HVDD = 10V, TA = -40~85°C (unless otherwise noted)

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SUPPLY CURRENT | ||||||

| IVDD | VDD supply current | VVDD = 5V, fOSC = 40 MHz | 3 | 6 | mA | |

| IVDD_IO | VDD_IO supply current | VVDD_IO = 3.3V | 3 | 6 | mA | |

| IHVDD | HVDD supply current | VHVDD = 10V, Fsw = 40 kHz | 5 | 10 | mA | |

| SUPPLY VOLTAGE | ||||||

| VVDD | VDD supply voltage range | 4.5 | 5.5 | V | ||

| VVDD_IO | VDD_IO supply voltage range | 1.6 | 5.5 | V | ||

| VHVDD | HVDD supply voltage range | 4.5 | 10 | 14.5 | V | |

| DIGITAL INPUTS/OUTPUTS (DIN, DOUT, SCLK, CS, SYNC) | ||||||

| VOL | Low-level output voltage | IOH = 4mA, VVDD_IO = 3.3V | GND + 0.25 | V | ||

| VOH | High-level output voltage | IOH = -4mA, VVDD_IO = 3.3V | VDD_IO – 0.6 | V | ||

| VIH | High-level input voltage | VVDD_IO = 3.3V | 2.1 | V | ||

| VIL | Low-level input voltage | VVDD_IO = 3.3V | 1.1 | V | ||

| IOH | 4 | mA | ||||

| IOL | -4 | mA | ||||

| SQUARE WAVE DRIVER (OUT [0] ~ OUT [63]) | ||||||

| IDOH_OUT | Output source current | Programmable in register DRV_OUT_SET [2:0] = 3b001 | 20 | mA | ||

| IDOL_OUT | Output sink current | Programmable in register DRV_OUT_SET [2:0] = 3b001 | 20 | mA | ||

| tjitter | Period jitter, determined by system clock | 40 | ns | |||

| COUT_Para | OUT parasitic capacitance when output config to be Hi-Z mode | 0.5 | pF | |||

| COM, REF DRIVER | ||||||

| IDOH_LYR | COM/REF driver source current | Programmable in register DRV_LYR_SET [2:0] = 3b001 | 20 | mA | ||

| IDOL_LYR | COM/REF driver sink current | Programmable in register DRV_LYR_SET [2:0] = 3b001 | 20 | mA | ||

| CLYR_Para | Parasitic capacitance when output config to be Hi-Z mode | 30 | pF | |||

| RESET THRESHOLD | ||||||

| VRST_HI | Reset input high threshold | 1.2 | V | |||

| VRST_LI | Reset input low threshold | 0.4 | V | |||

| SYSTEM PERFORMANCE | ||||||

| VHVDD_UVLO_F | HVDD falling to trigger HVDD undervoltage lockout | Register programmable to be disabled, with 3% accuracy | 4.2 | |||

| VHVDD_UVLO_R | HVDD rising to exist HVDD undervoltage lockout | Register programmable to be disabled, with 3% accuracy | 5 | V | ||

| VHVDD_OVLO_R | HVDD rising to trigger HVDD overvoltage lockout | Register programmable to be disabled, with 3% accuracy | 15.5 | V | ||

| VHVDD_OVLO_F | HVDD falling to exist HVDD overvoltage lockout | Register programmable to be disabled, with 3% accuracy | 15 | V | ||

| fCLK | Square wave driver clock frequency | Add external OSC as option | 38 | 40 | 42 | MHz |

| Vshort_th | Short detection threshold in self-test | 3.5 | V | |||

| tp | Driver propagation delay from SYNC active to 10% x HVDD, including 64 channels and COM | 1.25 | µs | |||

| tmismatch | Driver delay mismatch, including 64 channels and COM | 40 | ns | |||

| tsync | Minimum time of SYNC active | 0.5 | 1 | µs | ||

| tdata_ready | Data Ready pulse width | 4 | µs |

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SQUARE WAVE DRIVER (OUT [0] ~ OUT [63]) | ||||||

| tr | Driver rising time, 10% rises to 90% | Cload = 2.6nF, VHVDD = 5~12V | 1.25 | µs | ||

| tf | Driver falling time | Cload = 2.6nF, VHVDD = 5~12V | 1.25 | µs | ||

| SQUARE WAVE DRIVER (COM) | ||||||

| tr | Driver rising time | Cload = 10nF, VHVDD = 5~12V | 1.25 | µs | ||

| tf | Driver falling time | Cload = 10nF, VHVDD = 5~12V | 1.25 | µs | ||

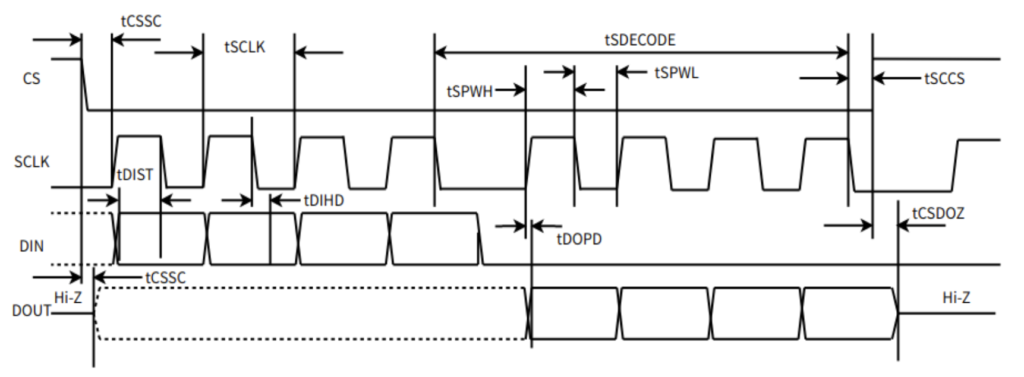

| SPI INTERFACE | ||||||

| fSPI | SCLK frenquency | 40 | MHz | |||

| tCSSC | CS low to first SCLK, setup time | 10 | ns | |||

| tSPWH | SCLK pulse high level width | 11 | ns | |||

| tSPWL | SCLK pulse low level width | 11 | ns | |||

| tDIST | Setup time, DIN valid to SCLK falling edge | 5 | ns | |||

| tDIHD | Holdup time, valid DIN after SCLK falling edge | 5 | ns | |||

| tDOPD | SCLK rising edge to DOUT valid | 9 | ns | |||

| tCS | CS high pulse | 20 | ns | |||

| tCSDOD | CS low to DOUT driven | 10 | ns | |||

| tSCCS | Eighth SCLK falling edge to CS high | 10 | ns | |||

| tSDECODE | Command decode time | 4 | ns | |||

| tCSDOZ | CS high to DOUT Hi-Z | 20 | ns |

MCAD0641 is an optical phased array driver. It generates up to 64-channels of programmable square wave signal to realize the beam steering, with 8-bit resolution.

For each output channel, MCAD0641 allows controlled independently and activated at the same time, and it uses 2 groups of registers to store the phase information of square wave output for overdrive mode and normal mode. All the outputs can be enabled or disabled individually by configuring the register bit. The output driver capability could be configured to obtain the best response time by providing up to 16 different selections.

MCAD0641 provides two outputs to control the top glass (COM) and reflection layer (REF) of the optical phased array. The COM and REF is allowed to be configured to be square wave, HVDD and HGND.

A unique diagnose circuit is also embedded to check that the short-circuit conditions of the optical phased array. 3 kinds of diagnose are provided the loop between channel to channel, the loop between channel to COM, and the loop between channel to REF. The test results are record in corresponding registers, and then the user could read and disable the failed channel selectively.

The built-in over-drive function can fasten the response time of the optical phased array. The square wave generator can run up to 78.12kHz with 8 different setting.

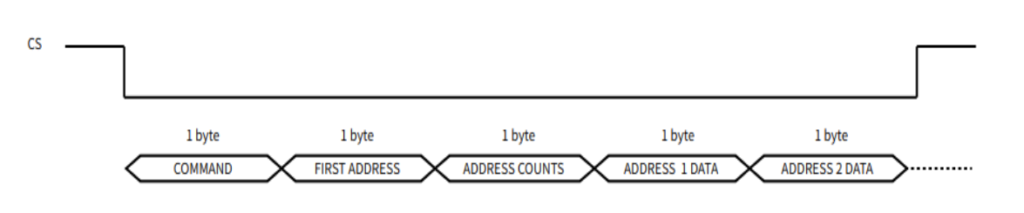

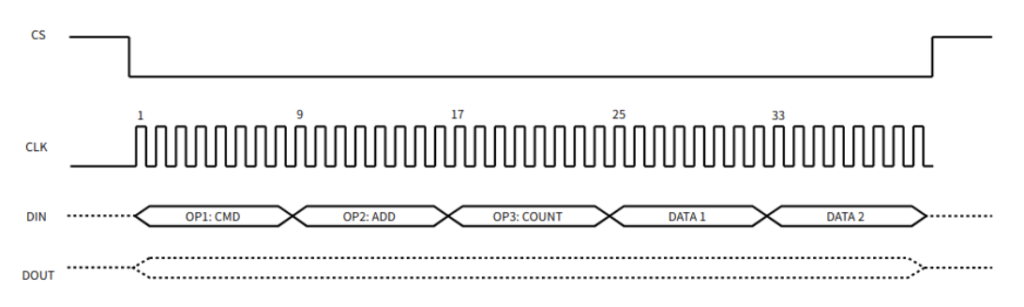

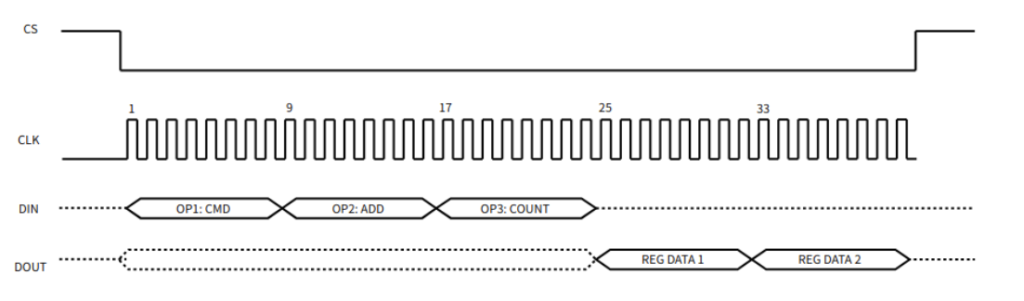

MCAD0641 is programmed through a standard SPI interface. The communication interface allows sequence read and write instructions. For typical application, the SPI master transfers 3 operation bytes and 128 data bytes to MCAD0641 slave in sequence to update the output related registers.

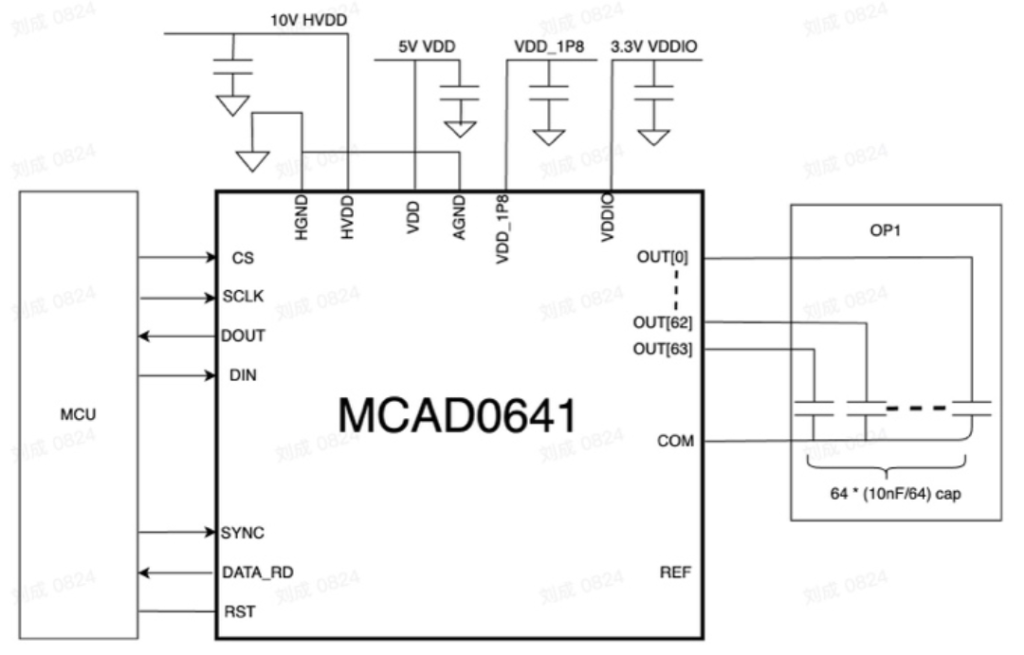

Three power supply rails should be provided for MCAD0641 for normal operation.

The VDD power is the external power supply, and it generates the AVDD power supply for the analog block and the VDD_1P8 is the power supply for the digital circuit through the internal 1.8V LDO. When VDD powers on, the chip will be POR.

HVDD is the external power supply as the power rail of the 64+1 channels PWM output. VDD_IO is the external power supply as the power rail of input and output interface.

Whatever any power supply power sequence, MCAD0641 could be powered on normally and stay in STANDBY state.

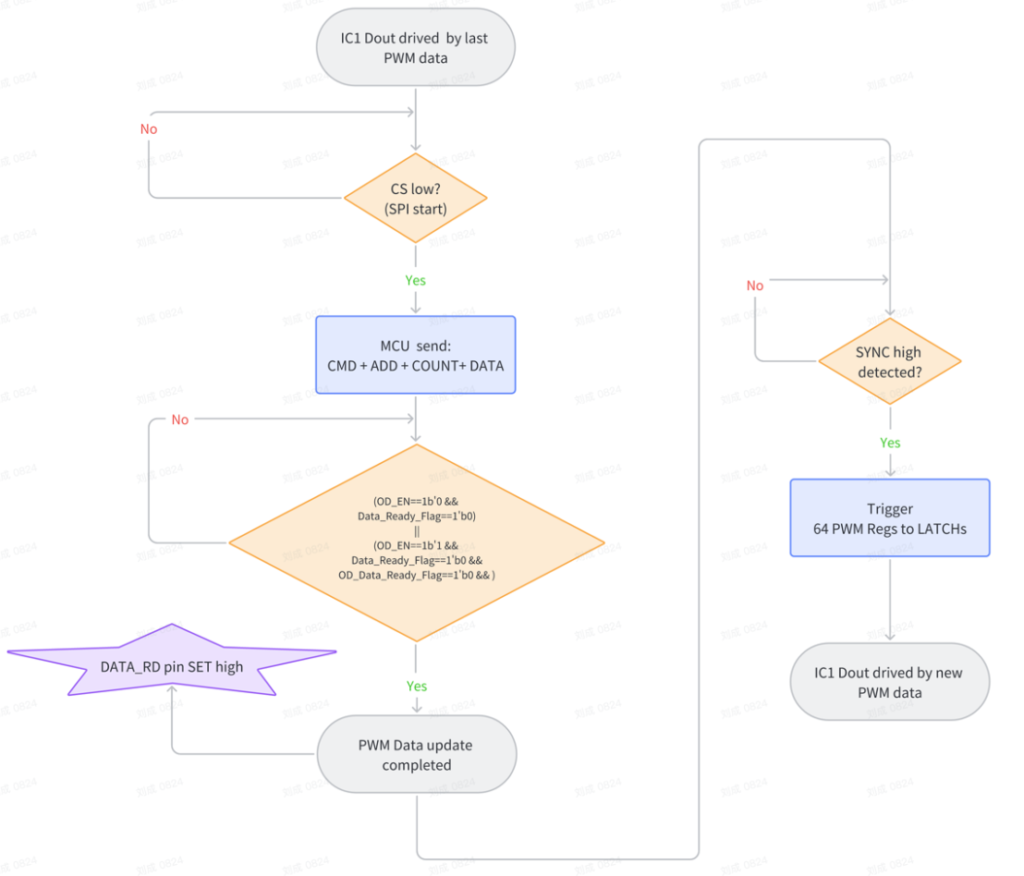

There are two WCLR registers located at the end of the data register block and the end of overdrive data register block. When OVERDRIVE_EN is high, DATA_RD is set high when Data_Ready_Flag is low and OD_Data_Ready_Flag reaches low. When OVERDRIVE_EN is low, DATA_RD is set high when Data_Ready_Flag reaches low.

After DATA_RD is set high, both Data_Ready_Flag and OD_Data_Ready_Flag are set to high.

In some unexpected application scenarios, MCAD0641 enters deadlock state accidentally. If the power supply of MCAD0641 can’t be cut off by software, then the deadlock state can’t exist in a packaged module.

To avoid this application scenario happening, the hardware reset function is integrated in MCAD0641 through RESET pin. Normally, RESET pin is pull-up to VDD with 100K internal resistor.

When there is a low level on the RESET pin longer than 0.5us, the whole chip will be reset. The reset function is same as the POR. The chip returns to the initial state as POR. Also, all the registers are reset.

COM and REF are two identical drivers. It can be biased to either HVDD or HGND. Also, it can be configured to be square wave output mode or Hi-Z mode.

Some short or open conditions may happen during manufacturing or application. It should report the short or open status through the register, then the master MCU can read the status and decide next operation.

During the application, if all these three bits is set 1 at the same time, the priority is as below:

There is potential risk that some of the OP1 channels (OUT [0:63]) are shorted to each other, so a self-test function is needed to find out the shorted channel and disable the corresponding driver output channel.

Here we assume only the adjacent channels could be shorted. We propose a solution to find out the shorted pair:

Switch on CH_X and CH_X+1

considered that short happening.

4. Record the status in the corresponding register.

Repeat it till all channels are tested. The shorted channels are recorded.

IC should figure out if there is a short condition between Channels and COM. Similar detection method as Channel-Channel:

Repeat it till all channels are tested. The shorted channels are recorded.

IC should figure out if there is a short condition between channels and reflection layer.

Similar detection method as Channel-Channel:

considered that short happening.

Repeat it till all channels are tested. The shorted channels are recorded.

The chips generate 64+1 square wave signals. There are 64 independent control lines and 1 COM line. All the square waves have the same frequency but different phase delays. The phase delay of COM line is always 0 degree.

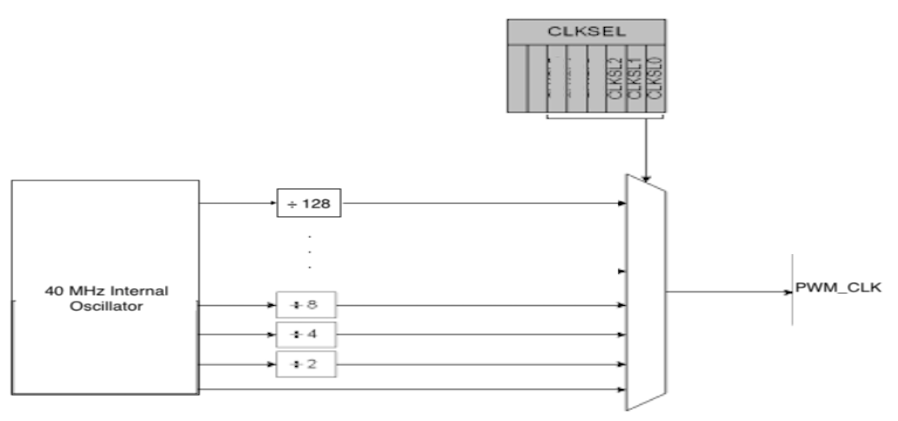

The square wave frequency can be configured based on the CLKSEL register, and it can be set as 0.61kHz, 1.22kHz, 2.44kHz, 4.88kHz, 9.77kHz, 19.53kHz, 39.06Hz, 78.12kHz.

The phase delay has 8-bit resolution to achieve 0–180-degree phase shift range. But in the application, only 180-degree range is needed.

Make sure data for new subframes are loaded to OVERDRIVE/PRESENT registers before sending out SYNC signal from master.

The values in PWM_OUTx are updated when SYNC signal changes from high to low. The PWM generator is reset at this point.

Data_RD is given when specific WCLR registers are written. It is used to indicate completion of data transmission to data registers and overdrive data registers. This signal is not in the main data process loop. It can be ignored. The refreshments of OUTx are controlled by SYNC only.

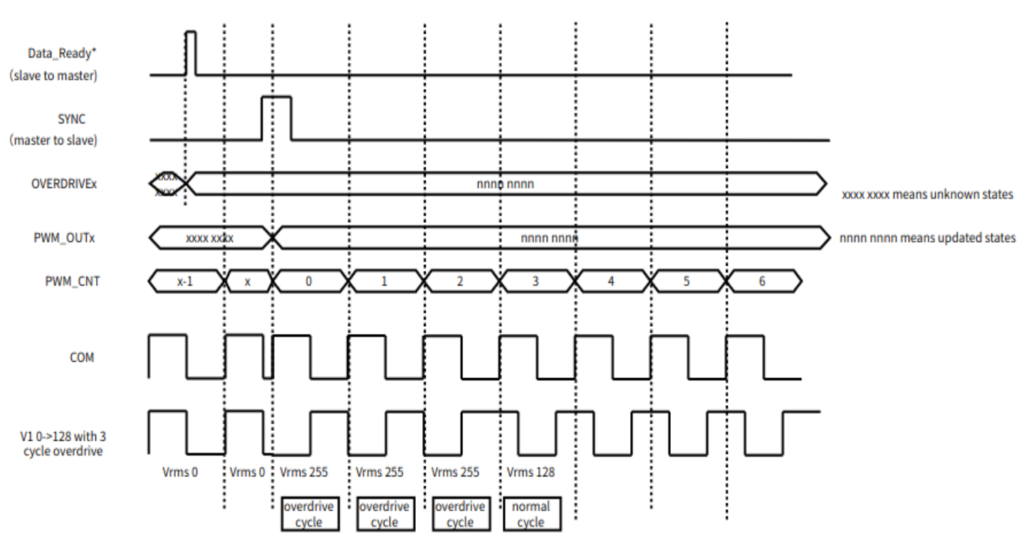

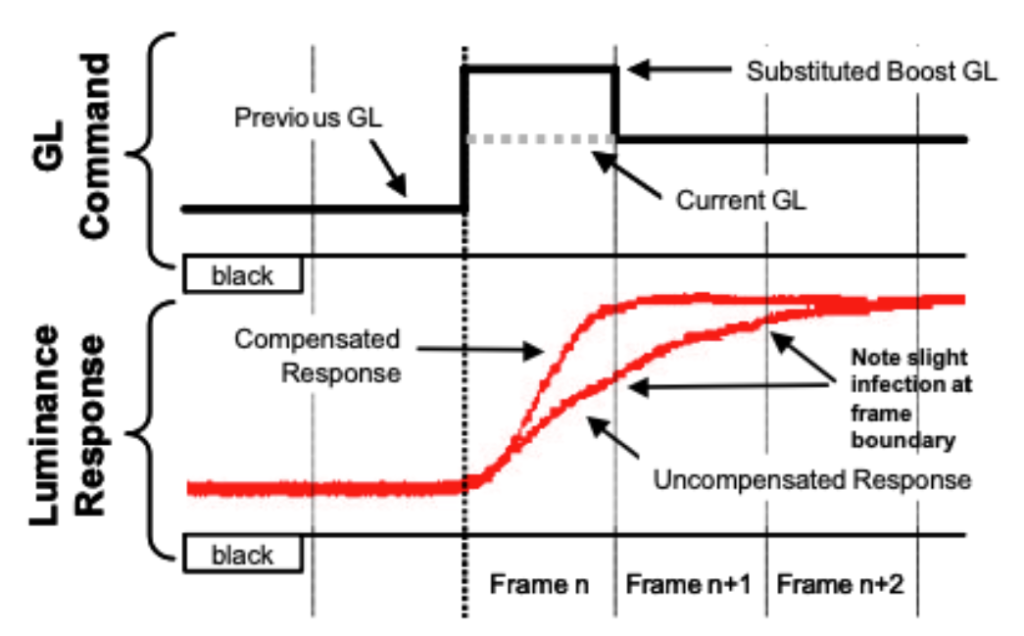

Due to the relationship between “applied voltage and response time” “applied voltage vs phase change” for optical phased array, if the phase change is small, the applied voltage should be small, and the response time will be long. To reduce the response time, a higher voltage can be inserted before the target voltage. This technique is called over-drive.

The figure below shows optical phased array response time compensation feature integrated in MCAD0641. GL is gray level, means to the applied voltage. This illustrates how the “substituted boost GL” (which is the over-drive voltage) reduces the response time.

In MCAD0641, the over-drive function is available when the user sets the register bit OD_EN=1. Also, the optional register is used to select the optimal over-drive cycles that the over-drive data lasts to obtain the best system performance.

Digital control and sequencer logic:

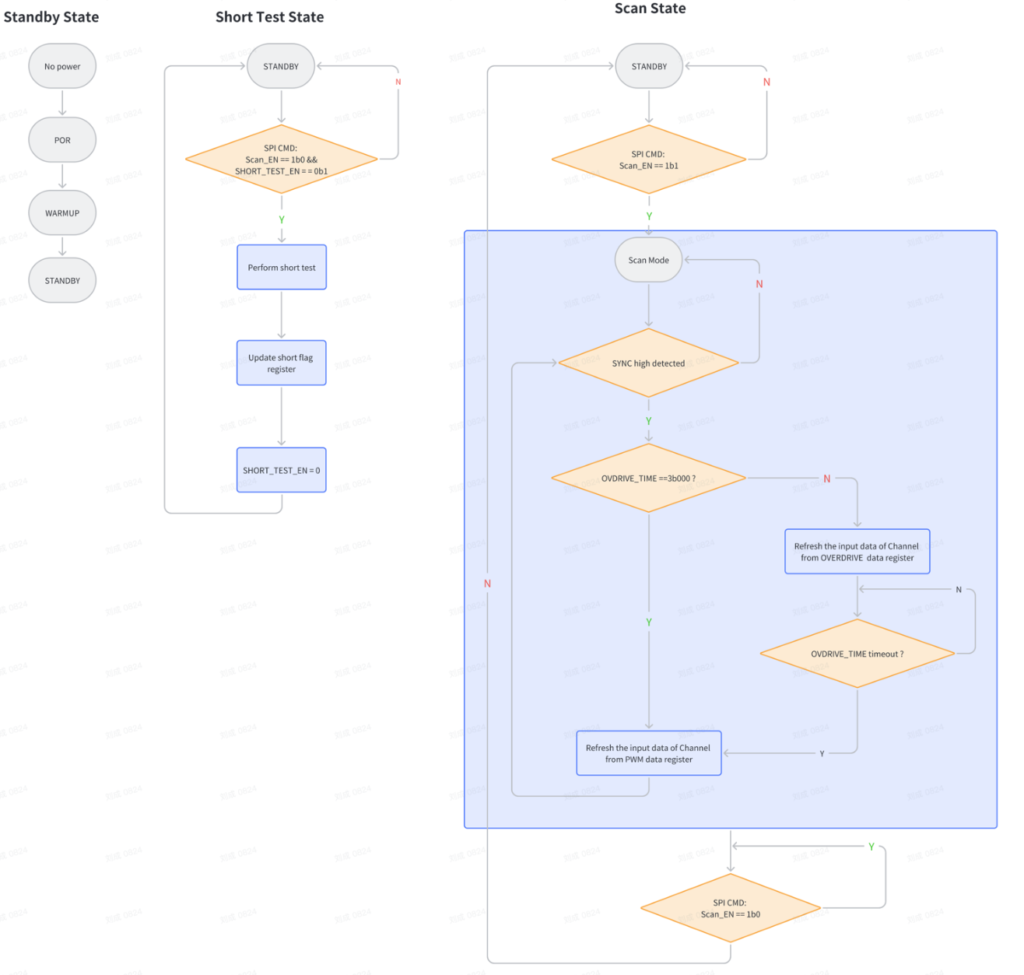

In Warmup state, default register values are loaded. The data interface is not responsive in this

state. After the warmup state is completed, MCAD0641 stays in standby state.

In STANDBY state all level shifter output stages are in a HiZ state. The device remains in STANDBY state if all enable registers (SCAN_EN, SHORT_CH_CH_TEST_EN, SHORT_CH_COM_TEST_EN, SHORT_CH_REF_TEST_EN) remains zero. All functions can be configured by data interface at this time. The master MCU shall read the test results and the channel status to check the functionality of MCAD0641 before proceeding to the next state.

When MCAD0641 receives short test command, it will initial a short test internally to check the status of the backward stage. Also, if not necessary in the application, the user can’t initial this test without the short test command.

During the short test mode, MCAD0641 finishes the channel-channel short test, channel-com short test, or channel-ref short test depending on the command of the master MCU.

After the short test is finished, MCAD0641 updates the status of the short status in the register and then goes back to standby mode. Also, the corresponding register bit is reset to 0 automatically.

When MCAD0641 enters scan state by the user’s command through SPI, it will send out the PWM signal based on the PWM data register. Every time SYNC goes to high, MCAD0641 will refresh the PWM information.

If the register bit OVERDRIVE_EN is set high, MCAD0641 will perform the overdrive data on the 64 output channels first, then switches to the PWM information based on the PWM data register.

The external microprocessor (master) communicates with the MCAD0641 chip via the SPI interface. The master sets application-specific chip configurations, triggers the measurements and reads the data. The SPI lines need to be connected according to the application diagram introduction.

The SPI-compatible serial interface consists of four signals: CS, SCLK, DIN and DOUT. The interface reads and writes registers, thus different commands to MCAD0641. There are two commands supported, RREG and WREG, which stand for reading registers and writing registers, separately. They are both multi-byte commands and the SPI transfer must follow a strict format in order to succeed.

For the application user, only READ and WRITE commands are available.

Also, the designer could enter backdoor or test mode if some unique commands are received. In backdoor mode, hidden registers can be read or written, not open to user applications.

In test mode, some tests are available in ATE or bench tests.

| Command | First CODE | Description |

|---|---|---|

| READ | 0xAA | Reads command |

| WRITE | 0x55 | Writes command |

| Backdoor | 0x5A | When receiving the first byte data 0x5A, it should be followed by 0xA5, 0x6F, 0xF6 to enter backdoor mode. Exit backdoor mode by setting CS high. |

| Test-Mode | 0x6F | When receiving the first byte data 0xA5, it should be followed by 0xF6, 0x5A, 0xA5 to enter test mode. Exit backdoor mode by setting CS high. |

SCLK is the SPI serial clock. SCLK is used to shift commands in shift data out from the device. The serial clock features a Schmitt-triggered input and clock data on the DIN and DOUT pins into and out of the MCAD0641. Even though the input has hysteresis, it is recommended to keep SCLK as clean as possible to prevent glitches from accidentally forcing a clock event.

When shifting in commands with SCLK, make sure that the entire set of SCLKs is issued to the device, as required by the command format. The timing between SCLK pulses can be loose, but the transfer will strictly follow the command format. If the interface goes to an unknown state, take RESET low to reset the transfer state and the internal registers.

The data input pin (DIN) is used along with SCLK to communicate with MCAD0641 (opcode

commands and register data). The device latches data on DIN on the SCLK falling edge.

The data output pin (DOUT) is used with SCLK to read register data from the MCAD0641. Data on DOUT is shifted out on the SCLK rising edge. DOUT stays in a high-impedance state when CS is high.

The device includes a 40MHz internal oscillator. Additional clocking options include the internal oscillator divided by 1 – 128. The system clock source is selected using the CLKSEL register.

For those applications that are not time-limited, the PWM frequency at 1kHz is recommended.

| CLCSEL | Clock Freq (MHz) | Square Wave Freq (kHz) | Minimum Response Time (µs) |

|---|---|---|---|

| 000 | 40 | 78.12 | 51.2 |

| 001 | 20 | 39.06 | 25.6 |

| 010 | 10 | 19.53 | 51.2 |

| 011 | 5 | 9.77 | 102.4 |

| 100 | 2.5 | 4.88 | 204.8 |

| 101 | 1.25 | 2.44 | 409.6 |

| 110 | 0.625 | 1.22 | 819.2 |

| 111 | 0.3125 | 0.61 | 409.6 |

Please see attached document for details.

Designers must pay close attention to PCB layout to achieve optimum performance for the

MCAD0641. Some key guidelines are as below:

| Orderable Device | Status | Package Type | Pins | MSL | Operation Temp (°C) | Device Marking |

|---|---|---|---|---|---|---|

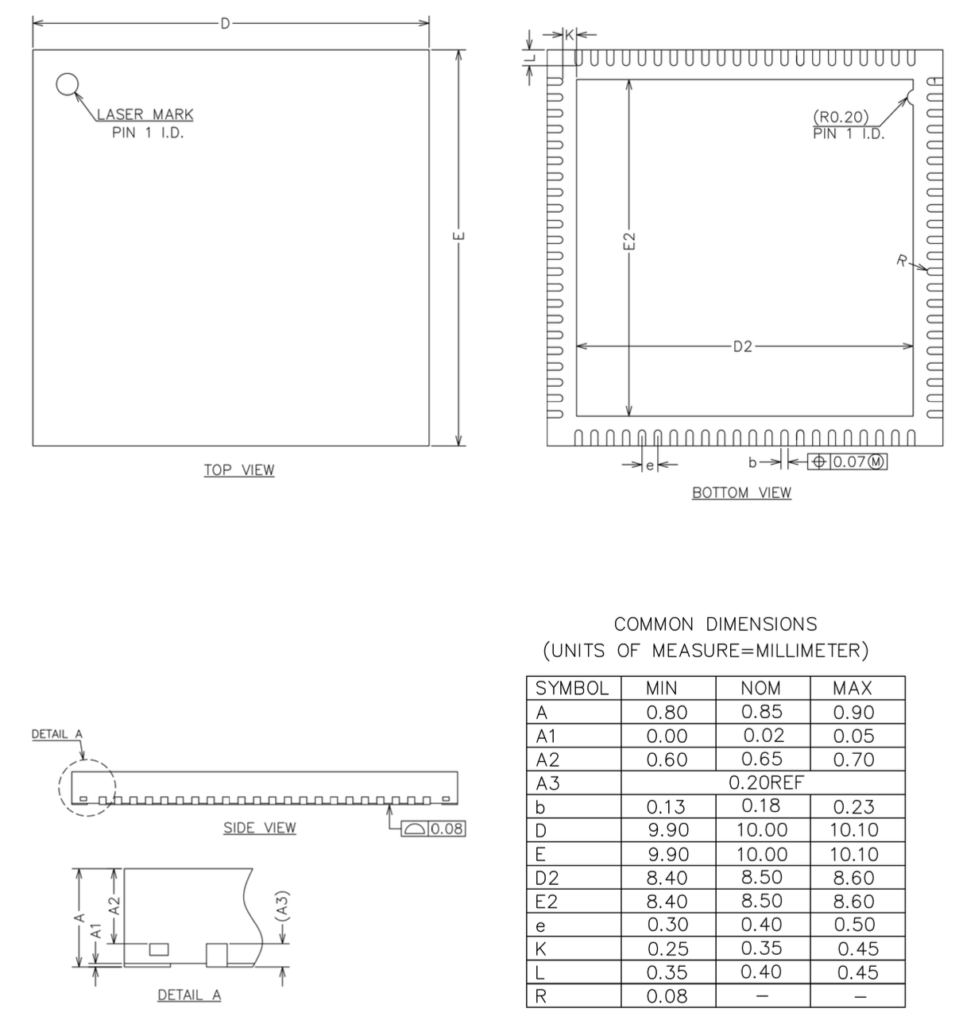

| MCAD0641 | Developing | QFN 10 x 10 | 88 | Level-3 | -40 to 125 | MCAD0641 |

(Preview) MCAE102-940 Metasurface Beam Steerer with 64 Independent Channels

(Preview) MMAE068-940 3D Time-of-Flight Camera with Meta Beam Steerer